Institut National Polytechnique

de Lorraine

E.N.S.E.M

THESE

présentée à

Laboratoire d'Electronique d'Electrolechnique et d'Automotique E. N. S. E. M. 2, Rue de la Citadelle B. P. 850 - Tél. 52.68.32 54011 NANCY CEDEX

L'I.N.P.L

pour l'obtention du titre de

DOCTEUR INGENIEUR

SPECIALITE INFORMATIQUE

par

Algin COCHET MUCHY

Ingenieur ENSEM

SUJET :

LA PRODUCTION DE PROGRAMMES

DANS LE PROJET SYGARE

Section Pocus entaire ZZ Section Pocus entaire ZZ ZY ENSEM

Service Commun de la Documentation INPL

Nancy-Bradois

Soutenue publiquement le 16 novembre 1978 devant la commission d'examen

D 136 035469 1

embres du jury

Président

M. C PAIR

Examinateurs :

M. C CAMOZZI

M. J.C DERNIANE

M. M GRIFFITHS

M. R HUSSON

M. J.P THOMESSE

1360354691

MISTS COCHET-TIUCHY A.

Institut National Polytechnique de Lorraine

E.N.S.E.M

Liberatoire deletronisme d'Electrotechnique endiament ligite E. N. S. E. M. 2. Rue de la Charlella

8.P. 850 - Tel. 50 68 33 54011 NANCY GELER

THESE

présentée à

L'I.N.P.L

pour l'obtention du titre de

DOCTEUR INGENIEUR

SPECIALITE INFORMATIQUE

par

Algin COCHET. MUCHY

Ingenieur ENSEM

SUJET:

LA PRODUCTION DE PROGRAMMES

DANS LE PROJET SYGARE

Soutenue publiquement le 16 novembre 1978 devant la commission d'examen

Service Commun de la Documentation INPL

Mancy-Brabois

Mombres du jury

Président

M. C PAIR

Examinateurs :

M. C CAMOZZI

M. J.C DERNIANE

M. M GRIFFITHS

M. R HUSSON

M. JP THOMESSE

Nous remercions vivement Monsieur le Professeur PAIR, Président de l'Institut National Polytechnique de Lorraine, qui a bien voulu patronner notre travail, et qui nous fait l'honneur de présider ce jury.

Nous exprimons notre gratitude à Monsieur le Professeur HUSSON pour son accueil au sein de l'équipe automatique du Laboratoire d'Electronique, d'Electrotechnique et d'Automatique de l'E.N.S.E.M., et pour l'intérêt qu'il nous porte en participant à ce jury.

Nous remercions Monsieur le Professeur DERNIAME pour les nombreuses suggestions et critiques constructives qu'il nous a formulées, tout au long de notre travail, et lors de la rédaction de ce mémoire.

Que Monsieur le Professeur GRIFFITHS, Directeur de l'Institut Universitaire de Calcul Automatique de Nancy, et Monsieur CAMOZZI, Responsable du Département Logiciel de la S.E.M.S., trouvent ici l'expression de nos remerciements pour l'honneur qu'ils nous font en participant à ce jury.

Nous remercions Monsieur THOMESSE, Responsable du projet SYGARE, pour ses conseils de tous les instants et pour l'ambiance amicale qu'il n'a cessé d'entretenir.

Nous exprimons notre sincère reconnaissance à Madame DALBOURG, et au personnel du D.P.I.C. de l'Institut National Polytechnique de Lorraine, qui ont assuré avec soin et diligence la réalisation matérielle de ce mémoire.

Nous remercions enfin tous nos collègues du Laboratoire E.E.A. de l'E.N.S.E.M. et du Centre de Recherches en Informatique de Nancy pour leurs conseils et leurs encouragements amicaux.

### TABLE DES MATIERES

## INTRODUCTION

## CHAPITRE I : LE PROJET SYGARE

- I.1. EVOLUTION DES AUTOMATISMES INDUSTRIELS

- I.2. QUELQUES LANGAGES TEMPS REEL

- I.2.1. Fortran Temps Réel

- I.2.2. Basic Temps Réel

- I.2.3. Procol

- I.2.4. RTL/2

- I.2.5. HAL/S

- I.2.6. Progress

- I.2.7. CPL1

- I.2.8. CORAL 66

- I.2.9. LTR

- I.2.10. PEARL

- I.2.11. Concurrent Pascal et Modula

- I.2.12. Divers

- I.2.13. Synthèse

## I.3. LES CARACTERISTIQUES DE SYGARE

- I.3.1. Décomposition d'une application dans Sygare

- I.3.2. Flux de données dans l'application

- I.3.3. Répartition de l'application sur le réseau

- I.3.4. Le système Gare

# CHAPITRE II : LA DESCRIPTION DES MODULES DANS SYGARE

- II.1. GENERALITES SUR LA PRODUCTION DE PROGRAMMES DANS SYGARE

- II.2. LE LANGAGE SOURCE

- II.2.1. Les objets de Sygare, les déclarations

- II.2.1.1. Déclarations de type

- II.2.1.2. Utilisation des données

- II.2.1.3. Attribut utilisateur

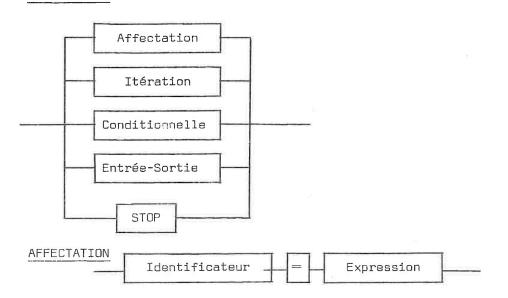

- II.2.2. Les instructions du langage

- II.2.2.1. Expressions et affectations

- II.2.2.2. Structures de contrôle

- II.2.2.3. Ordres d'entrée/sortie

- II.2.2.4. Divers

- II.2.2.5. Conclusion

### TI.3. LE LANGAGE INTERMEDIAIRE

- II.3.1. L'adressage en langage intermédiaire

- II.3.2. Les instructions du langage intermédiaire

- II.3.3. Caractéristiques du langage intermédiaire

### CHAPITRE III : LA COMPILATION DANS SYGARE

- III.1. INTRODUCTION

- III.2. LA COMPILATION

- III.2.1. Traitement des déclarations

- III.2.2. Traitement des instructions composées

- III.2.3. Traitement des expressions

- III.2.4. Traitement des entrées/sorties

- III.2.5. Divers

- III.2.5. Conclusion

# CHAPITRE IV : LA PRODUCTION DE CODE EXECUTABLE

- IV.1. PRINCIPE RETENU

- TV.2. ETUDE DE QUELQUES CAS DE GENERATION

- IV.2.1. Cas du Solar 16/40 SEMS

- IV.2.1.1. Présentation du matériel

- IV.2.1.2. Représentation des données et fonctions d'accès

- IV.2.1.3. Stratégie d'allocation de registres

- IV.2.1.4. Traduction des instructions intermédiaires

- IV.2.1.5. Gestion des conversions de données

- IV.2.2. Cas du Motorola M6800

- IV.2.2.1. Caractéristiques du matériel

- IV.2.2.2. Représentation des données

- IV.2.2.3. L'allocation des registres

- IV.2.2.4. Traduction des instructions intermédiaires

- IV.2.3. Cas du Intel 8080

- IV.2.3.1. Caractéristiques de la machine

- IV.2.3.2. Représentation des données

- IV.2.3.3. Traduction du langage intermédiaire

IV.2.4. Cas du Signétics 2650

- IV.3. ASSEMBLAGE ET TRAITEMENTS ANNEXES

- IV.4. SYNTHESE DES DIVERS CAS DE GENERATION

- IV.5. ECRITURE DES MACRO-DEFINITIONS

# CHAPITRE V : QUELQUES PARTICULARITES DE SYGARE

- V.1. LES OPERATIONS D'ENTREE/SORTIE DANS SYGARE

- V.2. REENTRANCE DES MODULES

- V.3. EXTENSION DU RESEAU PORTABILITE DU COMPILATEUR

- V.4. MISE AU POINT DES MODULES

## CONCLUSION

### BIBLIOGRAPHIE

### ANNEXES

ANNEXE I : LA SYNTAXE DU LANGAGE SOURCE DE SYGARE

ANNEXE II: LES MACRO-DEFINITIONS DU GENERATEUR DE CODE

ANNEXE III : EXEMPLE D'APPLICATION DECRITE A L'AIDE DE SYGARE :

COMMANDE D'UN MOTEUR PAS A PAS

## INTRODUCTION

Concevoir et réaliser une conduite de processus industriels, répartie sur un réseau de processeurs sans se préoccuper des contraintes occasionnées par cette répartition ; être déchargé de l'implantation et de la gestion des mécanismes informatiques de protection et de synchronisation ; tels sont les souhaits de nombreux automaticiens.

L'insuffisance des moyens actuellement disponibles, pour satisfaire ces désirs, est à l'origine du projet de SYstème de Gestion d'Applications temps réel REparties dont nous préciserons les caractéristiques essentielles (chapitre I).

Nous consacrerons ensuite notre étude à la fonction production de programmes du Système Gare, objet de notre travail.

L'utilisation d'un langage de programmation unique (chapitre 2) permet d'assurer la transparence de la réalisation vis à vis de la répartition.

L'obtention du code exécutable d'une application est décomposée en deux étapes :

- une compilation du langage source en un langage intermédiaire orienté machine (chapitre 3)

- une génération de code objet, paramétrée par le site d'exécution (chapitre 4).

Nous aborderons enfin quelques problèmes liés à la production de programmes, et leur incidence dans notre contexte particulier : mise au point, entrées/ sorties ... (chapitre 5).

CHAPITRE I

LE PROJET SYGARE

### LE PROJET SYGARE

## I.1. EVOLUTION DES AUTOMATISMES INDUSTRIELS

Le développement des automatismes dans l'industrie s'effectue actuellement à un rythme assez rapide. Il fut marqué tout d'abord par les progrès de la technologie remplacement des techniques analogiques par les techniques numériques souvent plus fiables et enfin passage de ces dernières à la logique programmée : commande par ordinateur, automates programmables. L'avènement récent du microprocesseur a encore accéléré ce phénomène par suite de son faible coût et de sa souplesse d'utilisation.

Parallèlement à cette évolution du matériel, et grâce aux possibilités nouvelles qu'il offre, de nouveaux concepts se sont dégagés pour la conduite des processus industriels : intégration de l'automatisation au niveau d'un atelier, d'une chaîne de production ; application de diverses stratégies de commande : commande répartie, commande centralisée, commande hiérarchisée, ...

De plus en plus, il sera demandé aux automatismes industriels de ne pas tenir compte uniquement des paramètres physiques des régulations, mais aussi de facteurs économiques par exemple : commande optimale, gestion de production ...

Ces évolutions conduisent très souvent à l'utilisation de plusieurs processeurs pour effectuer une conduite de processus et ceci pour diverses raisons dont les principales sont :

- utilisation des anciens matériels disponibles

- emploi de processeurs spécifiques pour certaines fonctions ou certains traitements

- conduite trop lourde pour un seul processeur

- doublement de certains processeurs pour des raisons de sécurité.

Ces divers processeurs forment alors un réseau généralement hétérogène dont on devra assurer la gestion afin d'y répartir la commande de processus désirée.

Ce contexte physique rejaillit sur la conception et la programmation des applications industrielles réparties, nous en retiendrons trois aspects spécifiques :

# \*programmation d'applications industrielles

Elle impose fréquemment l'utilisation de nombreux périphériques non standards,

d'unités de traitement spécialisées (traitement du signal, unités d'entrée/sortie et d'acquisition, automates programmables, machines à commande numérique). Elle nécessite des programmes sûrs et fiables, toute erreur pouvant avoir des conséquences graves. En outre l'utilisation fréquente de calculateurs dits "industriels" et de petite taille conduit à développer des programmes d'encombrement restreint. Les structures de données manipulées sont généralement très rudimentaires.

# <sup>™</sup>programmation temps réel

Les temps de réponse et de traitement doivent, dans de nombreux cas, être particulièrement courts ; cela conduit à une optimisation du code objet et à son adaptation à la machine par l'utilisation aussi complète que possible de toutes les possibilités matérielles qu'elle offre. Ce point est capital, car tout délai dans le contrôle du processus peut se traduire par une évolution dangereuse, et parfois irréversible, de celui-ci.

# "programmation d'applications réparties

Nous utilisons plusieurs matériels différents, donc aussi des systèmes d'exploitation différents. Il serait cependant souhaitable de concevoir l'application de manière unique, de disposer de possibilités de reconfiguration et de s'affranchir de la structure du réseau. Cela impose en particulier de décharger l'utilisateur de l'implantation des mécanismes informatiques imposés par la répartition (échanges intersites, synchronisation et gestion des données).

Les langages utilisés pour la programmation de conduite de processus industriels furent longtemps les langages d'assemblage, car on ne disposait alors de rien d'autre ; de plus cette méthode permettait de "coller" parfaitement à la structure des machines. Bien que largement utilisé encore, le langage d'assemblage présente de nombreux inconvénients :

- programmes peu fiables et difficiles à mettre au point

- manque de lisibilité des programmes rendant leur maintenance et leur évolution difficiles, surtout par d'autres personnels que le concepteur

- intransportabilité du produit ; empânhant en particulier toute reconfiguration, en cas de défaillance d'un site, si l'on ne dispose pas de plusieurs processeurs identiques.

Ces diverses raisons, liées à des contraintes économiques, ont conduit à l'élaboration de plusieurs langages de haut niveau dits "Temps Réel" et essayant de pallier ces inconvénients. Certains sont nés de besoins précis dans un domaine donné, ce sont les langages "orientés-problème", d'autres se veulent plus généraux. Examinons maintenant les caractéristiques de quelques uns parmi les plus répandus (/15/,/16/,/17/).

### I.2. QUELQUES LANGAGES TEMPS REEL

La plupart des langages décrits ci-après décomposent une application industrielle en un ensemble de tâches concurrentes.

Nous essayerons de préciser pour chaque langage, outre ses caractéristiques générales, les moyens mis en oeuvre pour assurer la gestion des tâches, implanter les protections et synchronisations et réaliser les opérations d'entrée/sortie.

# I.2.1. Fortran Temps Réel

L'un des premiers langages temps réel à être apparu est certainement le Fortran temps Réel. Il est obtenu par extension du Fortran classique, non par adjonction d'ordres nouveaux, mais par insertion d'appels de sous programmes spécifiques fournis par les constructeurs. Les interfaces d'appels de ces sous-programmes sont normalisés ce qui permet de ne pas rendre le Fortran temps Réel plus intransportable que le Fortran classique (/15/, /16/, /32/).

Les principales options introduites concernent :

- gestion élémentaire des tâches

- entrées-sorties industrielles

- manipulation des chaînes de bits

- gestion (limitée) du temps.

Malgré son manque de souplesse, ce langage est largement utilisé car il est disponible sur la plupart des ordinateurs.

# I.2.2. Basic Temps Réel

Le Basic temps Réel est un langage prévu pour être interprêté. C'est en fait une extension du Basic classique dont les performances sont spécialement étudiées pour une exécution dans un contexte temps Réel. Les entrées/sorties disponibles sont adaptées aux normes CAMAC (industrie nucléaire) ce qui en limite le champ d'utilisation (/16/, /40/).

# T.2.3. Procol

Ce langage a été effectivement conçu pour le temps Réel. Il permet un certain nombre de facilités :

- description de la configuration utilisée

- gestion des tâches

- synchronisation

- entrées/sorties industrielles.

Cela est obtenu par l'utilisation d'instructions spéciales permettant

également la manipulation d'événements, de sémaphores, de ressources conjointement avec des instructions plus classiques inspirées de Fortran.

Une application est décomposée dans le système Procol en un ensemble de tâches bénéficiant de compilations séparées. Une section spéciale compilée à part et nommée "COMMON" permet de décrire la configuration de l'application : périphériques spéciaux, traitements de données ... Ces informations sont valables pour toutes les tâches.

Les structures de données disponibles en Procol sont également inspirées de Fortran, avec une extension en ce qui concerne les chaînes de bits.

Les entrées-sorties sont obtenues par des instructions analogues à celles de Fortran, munies de spécification de format décrivant les traitements à faire subir aux données (faisant éventuellement référence aux informations de la section COMMON).

On dispose enfin de la possibilité d'insérer du langage d'assemblage pour traiter tous les cas particuliers.

L'utilisation de Procol nécessite un système d'exploitation associé. Ce langage est implanté essentiellement sur T 2000 et Mitra (/16/, /17/, /1/).

# I.2.4. RTL/2

La programmation d'une application en RTL/2 s'effectue sous forme de modules dotés d'une structure de bloc. RTL/2 permet de manipuler des données de types multiples :

- octet

- réel

- fractionnaire

- pointeurs de piles et de blocs

de manière isolée, en tableaux de variables de même type ou en enregistrements de variables et tableaux de types quelconques.

Les instructions comprennent :

- opérateurs arithmétiques et logiques

- décalages

- branchements (GO TO)

- affectations

- itérations (FOR ... WHILE ...)

- conditionnelles (IF ...)

- gestion des tâches et entrées/sorties par appel superviseur.

Le code généré est réentrant, il est obtenu après passage par un langage intermédiaire de type assembleur.

On peut éventuellement insérer du code objet directement dans RTL/2. Le langage RTL/2 est développé en Grande-Bretagne par ICL (/6/).

# I.2.5. HALS/S

Le langage temps Réel HALS/S est l'exemple même du langage brienté problème"; il a été développé pour l'aéronautique par la NASA et l'agence Spaciale Européenne.

HALS/S est dérivé de PL/1 et d'Algol 60 dont il reprend la partie algorithmique et la structure de bloc.

Il fournit à l'utilisateur un jeu d'instructions élaborées permettant la gestion des tâches, des événements, des données (zones de données à accès contrôlé), ainsi que des facilités d'algèbre linéaire nécessaires aux logiciels de guidage /5/.

# I.2.6. Progress

Progress est un langage inspiré de PL/1 et d'Algol 68 en ce qui concerne la partie algorithmique. Il autorise l'utilisateur à définir ses propres types de données en plus des types standards (entier, fixe, flottant, bit, caractère).

Le langage fournit un jeu d'instructions spécialisées pour la gestion des tâches, des événements (synchronisation) et des ressources. Progress différencie les conditions d'exécution des tâches en distinguant les procédures synchrones des modules asynchrones.

Progress essaye d'optimiser l'occupation de la mémoire en réalisant une allocation dynamique pour les divers segments de données ou de code selon une méthode inspirée de Multics /48/, /50/.

# I.2.7. CPL1

Le langage CPL1 est un sous langage de PL1. CPL1 veut être facilement portable et à faible taux d'expansion, il élude de ce fait un certain nombre de problèmes spécifiques des divers matériels, en particulier les entrées-sorties et la gestion de tâches. Il peut cependant être utilisé comme langage "temps Réel" car il est extensible et permet à l'utilisateur de définir toutes les instructions lui manquant pour manipuler les périphériques et mécanismes de synchronisation de son installation.

Le code généré par CPL1 est un code virtuel qui doit être "macrodéfini" sur chaque machine. L'optimisation de ce code tient, pour une bonne part, aux restrictions imposées au programmeur : ainsi les expressions mixtes sont interdites /7/.

# I.2.8. CORAL 66

La conception du langage Coral 66 a été orientéevers la génération d'un code rapide à l'exécution, le taux d'expansion du compilateur étant faible. Comme pour CPL1, ce langage ne possède pas directement d'instructions temps Réel. Il peut cependant acquérir les possibilités des autres langages en autorisant l'écriture de procédures ou de macro-instructions réalisant les fonctions désirées. Les instructions de Coral 66 sont celles d'Algol 60 avec possibilité de manipulation de bits, d'insertion de code et de macro-instructions. Les programmes Coral 66 sont munis de la structure de bloc.

Ce langage est assez largement répandu en Grande-Bretagne /6/.

## I.2.9. LTR

LTR est un langage adapté à la programmation structurée. Une application est décomposée en plusieurs articles :

- les données moniteur (événements, ressources, périphérie ...)

- les données générales

- les procédures communes

- les données, procédures, initialisations, procédures d'interruptions.

Les instructions du langage permettent la programmation temps Réel grâce aux notions d'événement, de ressource, de délai, d'interruption. Elles permettent l'utilisation de structures de données assez complètes : variables de type entier, fixe, flottant, binaire, caractère, pointeur, ... sous forme de variable simple, de tableau, de structure simple, de tableau de structures, d'ensembles dynamiques.

Les entrées-sorties peuvent s'effectuer de diverses manières :

- directement par le programme

- sous contrôle du superviseur

- avec formattage des données

- entrée-sorties spécifiques sur périphérie spécialisée.

Le code est généré avec passage par un langage intermédiaire et optimisation à ce niveau /3/.

# I.2.10. Pearl

La programmation d'une application en Pearl est composée de deux sections :

- une section système qui décrit le matériel utilisé : périphériques, interruptions ... - une section programme écrite avec des instructions inspirées de Fortran et d'Algol. On dispose également d'ordres d'activation et de synchronisation de tâches.

Les instructions MOVE, GET et PUT permettent d'effectuer des entrées/ sorties sur tous types de périphériques en mode formatté ou non.

La génération de code peut se faire sur plusieurs machines à l'aide d'un "macro-processeur". Les machines utilisées sont cependant de types assez voisins.

Ce langage est assez répandu en R.F.A. /2/, /8/.

## I.2.11. Concurrent Pascal et Modula

Concurrent Pascal et Modula ne sont pas des langages temps Réel au sens habituel de l'expression. Ce sont deux langages inspirés de Pascal et adaptés à la programmation du parallélisme sur les multiprocesseurs.

Modula permet en outre de gérer assez facilement des entrées-sorties spéciales bien que cela ne fasse pas partie intégrante du langage /16/, /22/.

# I.2.12. Divers

A ces langages plus ou moins largement répandus, il faut ajouter divers langages d'utilisation plus restreinte :

- PL/16 langage évolué conservant les possibilités de l'assembleur : accès aux registres, utilisation de toutes les instructions de la machine et à tous les niveaux d'information (bit, octet, mot). Ce langage est implanté sur les gammes T1600 et Solar. Il n'est pas transportable car bâti autour du matériel /16/, /36/.

- PL/M langage de haut niveau développé pour les microprocesseurs par Intel et Motorola /16/.

- Langages d'automates programmables (ex. APILOG /38/).

Il faut enfin noter que de nombreuses études sont en cours pour essayer de définir un langage vraiment adapté au temps réel notamment en ce qui concerne l'expression du parallélisme et des synchronisations entre tâches /23/,/41/,/46/,/47/,/54/.

# I.2.13. Synthèse

Les langages que nous venons d'étudier satisfont généralement les

deux premiers points que nous avons exposés : programmation d'applications industrielles en temps réel. Ils présentent d'autre part un certain nombre de points communs. Tout d'abord les synchronisations entre tâches sont exprimées, de diverses manières, à l'intérieur même des programmes rendant ainsi délicate toute modification de l'application. La gestion des protections, mécanismes d'accès aux données, etc. sont facilités mais toujours à la charge de l'utilisateur avec tous les risques de mauvaise utilisation que cela implique.

Remarquons enfin que la plupart de ces langages sont orientés vers une gamme de machines et ne sont pas effectivement transportables (nécessité d'un système d'exploitation associé par exemple) ou s'ils le sont, c'est au détriment du service à l'utilisateur (CPL/1 ...).

Lorsque la conduite de processus doit être répartie, ces langages ne permettent plus de satisfaire le troisième point que nous avions défini : ils imposent une répartition à priori des différentes fonctions sur les divers sites et de plus ne permettent pas d'exprimer les relations entre les processeurs du réseau, car ils sont conçus dans un contexte monoprocesseur ou multiprocesseur à mémoire commune (Modula ...).

La gestion du réseau doit alors être effectuée par des procédures écrites en langage assembleur ; il convient d'ailleurs de remarquer que nous ne disposons pas encore d'outils très développés pour cela, les récents progrès dans ce domaine étant orientés vers d'autres préoccupations : télétraitement, gestion, etc. /26/, /39/, /40/.

Ces diverses lacunes ont été à l'origine du projet Sygare pour la conception et la réalisation de conduites réparties en temps réel de processus industriels.

### I.3. LES CARACTERISTIQUES DE SYGARE

Le projet Sygare a été conçu pour aider l'automaticien dans la conception et la réalisation de systèmes répartis de conduite de processus industriels /43/. Dans ce but, il met à sa disposition divers outils qui permettent :

- de décrire et structurer l'application,

- de la programmer,

- de l'implanter et de la faire évoluer selon les besoins.

Ces divers outils rendent transparents, quand cela est possible, l'architecture du réseau et les mécanismes informatiques mis en œuvre.

# I.3.1. Décomposition d'une application dans Sygare

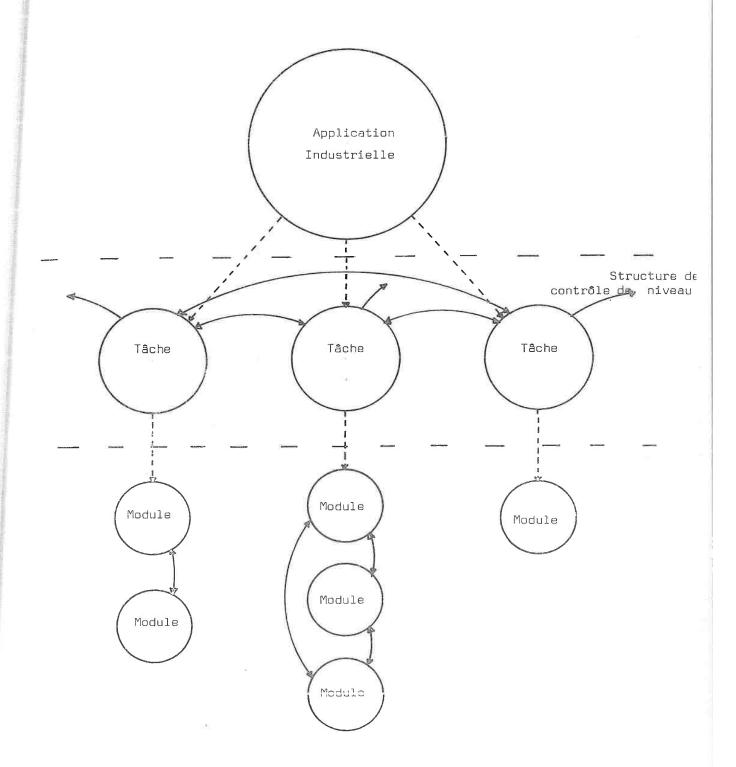

Une application industrielle peut généralement être considérée comme un ensemble de processus physiques se déroulant en simultanéité, cela se traduira dans Sygare par leur implantation sous forme de tâches logicielles parallèles. Ces tâches seront synchronisées entre elles et par rapport au milieu extérieur à l'aide de structures de contrôle appelées "structures de contrôle de niveau 3".

Une tâche peut dans la plupart des cas être scindée en divers sousensembles fonctionnels ou modules correspondant à des actions élémentaires. L'enchaînement des modules à l'intérieur d'une tâche est alors exprimé par des structures de contrôle spécifiques dites : "structures de contrôle de niveau 2".

Le module est l'élément de base de Sygare pour :

- la compilation,

- la répartition sur le réseau,

- l'exécution.

Le langage de programmation de ces modules constitue le niveau 1.

Ce fractionnement en tâches et modules présente le double avantage de correspondre à une décomposition naturelle de l'application industrielle, et de permettre une description et une programmation modulaires de celle-ci /34/ (fig.I-1).

Une caractéristique essentielle du projet Sygare est que toutes les liaisons entre les modules apparaissent explicitement et uniquement à l'extérieur de ceux-ci, simplifiant ainsi considérablement l'évolution future de l'application /52/.

# I.3.2. Flux de données dans l'application

Chaque module de Sygare peut être considéré comme un automate. Il possède des entrées et des sorties : les variables qui lui permettent de communiquer avec les autres modules, et il est caractérisé par un algorithme, utilisant les structures de contrôle du niveau 1, qui exprime l'évolution des sorties et de l'état final, en fonction des entrées et de l'état précédent.

Nous voyons apparaître ici un autre aspect de Sygare : la description du flux de données dans l'application. En effet, la mise en correspondance des entrées et sorties des modules est faite entièrement à l'extérieur de ceux-ci à l'aide de déclarations de connexions appartenant au langage de niveau 2. Ces déclarations qui décrivent la circulation des informations dans l'application permettent, conjointement avec les structures de contrôle de niveau 2 et 3, d'en déterminer les

Fig. I.1. Décomposition d'une application industrielle de Sygare.

conditions d'utilisation. C'est grâce à elles que le moniteur d'exploitation pourra établir les mécanismes de protection et d'accès aux données ; ces accès sont en effet spécifiques de chaque utilisation (accès en exclusion mutuelle, duplication d'informations, mises à jour entre sites ...) /53/.

Les connexions interagissent aussi sur les conditions d'activation des modules et sont utilisées lors de la mise en place des synchronisations. L'implantation automatique de ces mécanismes de protection et de synchronisation est une autre particularité de Sygare qui contribue très largement à l'amélioration de la fiabilité de l'application /52/, /53/.

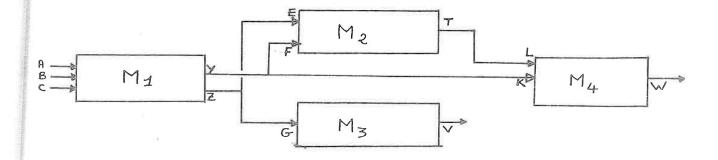

L'exemple ci-dessous nous aidera à mieux comprendre le rôle de ces déclarations de connexion.

Exemple: Considérons quatre modules.

M1 d'entrées A, B, C de sorties Y, Z

M2 " E, F " T

M3 " G " V

M4 " K, L " W

Le flux d'informations :

est décrit par les déclarations de connexions :

Y de M1 → F de M2

Z de M1  $\rightarrow$  E' de M2

Y de M1  $\rightarrow$  K de M4

Z de M1  $\rightarrow$  G de M3

T de M2  $\rightarrow$  L de M4

On remarquera que la description du flux ne dépend pas directement des conditions d'activation des modules, ainsi avec les connexions ci-dessus on peut avoir divers

## enchaînements:

M1 suivi de M2 // M3

M1 " de <u>Si</u> condition <u>Alors</u> M2 Sinon M3

M1 " de M2 suivi de M3

La seule condition à remplir étant bien sûr d'avoir produit la donnée avant de la consommer.

# I.3.3. Répartition de l'application sur le réseau

Les choix d'implantation des divers modules et tâches sur les différents processeurs du réseau sont exprimés indépendamment de la description de l'application qui est donc totalement libérée des contraintes de répartition.

L'utilisation d'une description de l'application scindée en plusieurs niveaux de fonctionnalités différentes permet de remettre plus facilement en cause les choix initiaux et facilite l'évolution ultérieure du système (nouvelle répartition des modules sur le réseau, introduction de nouveaux modules ...).

La transparence de la répartition des modules lors de la conception de l'application est également assurée en ce qui concerne les opérations d'entrée/sortie par l'utilisation d'ordres unifiés traitant les échanges avec la périphérie conventionnelle ou industrielle (sur le site ou à distance), d'assignation de périphériques et de moniteurs d'entrée/sortie locaux interconnectés.

# I.3.4. Le système Gare

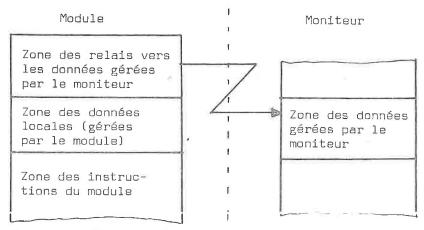

Le système Gare est composé de deux parties essentielles :

"Un moniteur d'exploitation réparti qui assure la gestion du réseau, des communications entre sites, l'implantation des mécanismes de protection des données et de synchronisation, l'interprétation des structures de contrôle de niveau 2 et 3, des déclarations de connexion, des commandes opérateur d'activation et de contrôle de l'application, des déclarations de répartition des modules /42/.

"Un système de production de programmes qui fournira au moniteur d'exploitation le code binaire exécutable des divers modules de l'application sur les divers sites du réseau, et permettra l'archivage, l'évolution et la documentation de ces mêmes modules. C'est ce système que nous allons maintenant étudier plus en détail.

# CHAPITRE II

LA DESCRIPTION DES MODULES DANS SYGARE

### CHAPITRE II

# LA DESCRIPTION DES MODULES DANS SYGARE

# II.1. GENERALITES SUR LA PRODUCTION DE PROGRAMMES DANS SYGARE

La fonction production de programmes est celle qui permet la description des modules, leur traduction en code exécutable, leur archivage, leur documentation et leur évolution.

Cette fonction nécessite le choix d'un langage de programmation qui nous servira à décrire les modules. Compte-tenu des buts que nous nous sommes fixés et des remarques faites au chapitre précédent, ce langage doit être le même pour tous les sites du réseau, et de haut niveau, afin de garantir une certaine fiabilité et une programmation de l'application indépendante de sa répartition. Pour les mêmes raisons, nous n'autoriserons pas l'insertion de code objet dans le texte des modules, contrairement à la majorité des langages temps réel /16/. Le langage retenu ne possèdera pas non plus d'ordres d'activation de modules et de gestion de tâches, ceuxci étant reportés à l'extérieur des modules dans les structures de contrôle de niveaux 2 et 3.

La traduction de ce langage source en code exécutable pourrait se faire directement; elle nécessiterait alors autant de compilateurs que de types de sites sur le réseau (ou un compilateur à sorties multiples). Cette solution est peu intéressante car elle n'est pas souple et ne permet en particulier pas d'étendre simplement le réseau puisqu'il faut écrire de nouveaux compilateurs. Il convient d'autre part de remarquer que de nombreux traitements du langage source sont valables pour tous les sites :

- détection d'erreurs

- analyse lexicographique et gestion de la table des symboles

- analyse syntaxique.

Cela conduit à diviser la production du code exécutable en deux étapes /8/, /9/, /10/. :

- une compilation du langage source en un langage intermédiaire orienté machine, mais cependant indépendant de celle-ci

- une génération de code objet paramétrée par le site d'exécution.

L'adoption d'un langage intermédiaire présente en outre de nombreux avantages.

- \* Capacités de stockage réduites pour la conservation des modules

- \* Extension simplifiée du réseau : la première partir du traitement, la compilation, ne change pas, il reste à créer un générateur de code pour le nouveau site introduit /9/.

- "Traduction rapide et aisée du langage intermédiaire en langage machine, l'analyse syntaxique et la détection des erreurs sont déjà effectués, cette possibilité est intéressante en cas de reconfiguration dynamique de l'application.

- → Possibilité à partir du même langage intermédiaire et pour un site donné,

de générer divers types de code objet

- \* Possibilité d'effectuer une simulation des modules au niveau du langage intermédiaire.

- \* Possibilité de disposer de bibliothèques de fonctions prédéfinies en langage intermédiaire, ce qui accélère et facilite le traitement lors de la compilation.

La production des programmes s'effectue dans Sygare sur un site unique. En effet, la plupart des calculateurs industriels disposent de configurations réduites et inadaptées à cette fonction, il suffira d'équiper une machine des moyens nécessaires. Le site choisi peut ou non participer lui-même à la conduite des processus. De plus, la fonction production de programme ne nécessite pas les mêmes impératifs de sécurité que la conduite proprement dite et sa défaillance momentanée est parfaitement tolérable dans la majorité des cas.

Le site de production est doté, en plus des traducteurs proprement dits, d'un ensemble de processeurs logiciels permettant la gestion, la conservation et la documentation des modules tant au niveau du langage intermédiaire (modification de la répartition, reconfiguration dynamique) qu'au niveau du langage source, afin de permettre une évolution aisée de l'application /34/.

### II.2. LE LANGAGE SOURCE

Nous avons adopté un langage source inspiré des divers langages algorithmiques déjà cités (chapitre I). Notre but n'étant pas de définir un nouveau langage mais une méthode de production de programmes pour une application répartie, il conviendra de considérer que le langage présenté, ci-après, est une version minimum non figée. Nous suggérons d'ailleurs diverses améliorations possibles pour une plus

grande clarté de programmation et une meilleure détection des erreurs.

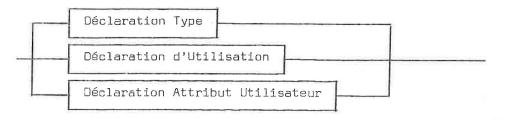

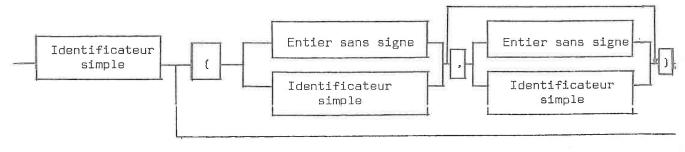

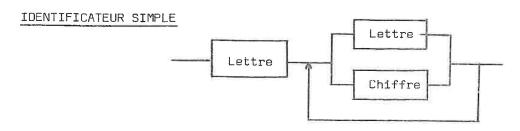

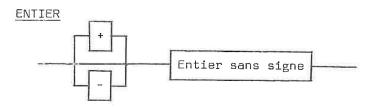

# II.2.1. Les objets de Sygare. Les déclarations

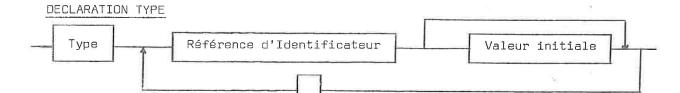

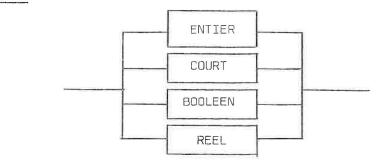

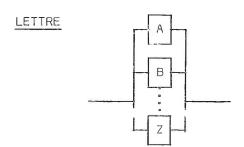

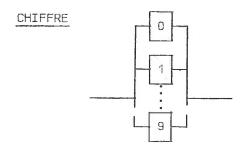

# II.2.1.1. Déclarations de type

Les structures de données adoptées sont volontairement très simples et inspirées de FORTRAN, ce sont :

- variables simples

- vecteurs de variables simples ou tableau à 1 indice

- tableaux de variables simples à 2 indices.

L'imbrication de ces structures est interdite, c'est à dire qu'un indice de tableau ne peut être lui-même un élément de tableau.

Les variables simples appartiennent à des types prédéfinis qui sont au nombre de quatre :

- entier

- réel

- booléen

- entier court (octet)

Ce dernier type ayant été introduit pour permettre une optimisation du code généré sur de nombreux mini-ordinateurs (utilisation de l'adressage immédiat) et sur les microprocesseurs dont les modèles les plus courant travaillent au niveau de l'octet.

Une plus grande souplesse pourra être apportée par l'introduction de deux types supplémentaires :

- chaînes de caractères

- chaînes de bits.

Pour faciliter la détection ultérieure d'erreurs, toutes les variables utilisées dans un module doivent être préalablement déclarées à l'aide d'un jeu de déclarations spécifiques permettant de préciser également la structure retenue :

ENTIER liste

REEL

BOOLEEN "

COURT

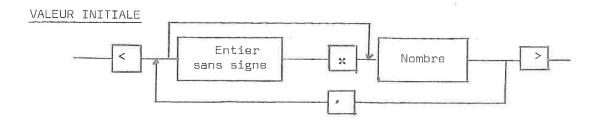

où liste représente une suite d'identificateurs de variables simples ou de tableaux (il faut alors déclarer leurs dimensions). Il est en outre possible d'attribuer,

lors de leur déclaration, une valeur initiale à ces variables (cette option est analogue à l'ordre DATA de FORTRAN) :

exemple: ENTIER ITAB(5)<3%3,1,70>,K,J<7>

BOOLEEN BOOL<'V'>

Les déclarations ci-dessus définissent trois variables simples K, J, BOOL et un tableau. Seule la variable K n'est pas initialisée. Le tableau ITAB correspondra au lancement du module à l'organisation suivante :

| ITAB(1) | 3  |

|---------|----|

|         | 3  |

|         | 3  |

|         | 1  |

| (5)     | 70 |

Nous n'avons pas offert à l'utilisateur de structures des données évolutives (tableaux à dimensions variables par exemple) car elles nécessitent des méthodes d'accès dynamiques généralement coûteuses en place et en temps et nous pensons que cela est en contradiction avec les buts à atteindre. Par ailleurs, ce genre de structure est d'une utilité assez faible pour la plupart des applications industrielles.

Nous suggérons enfin la possibilité de déclaration du domaine de variation des données ce qui permettrait un contrôle renforcé de l'exécution et éventuellement une optimisation du code généré /18/, /25/.

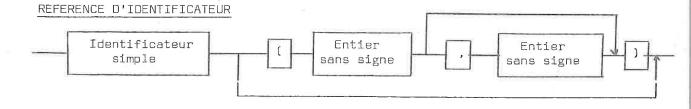

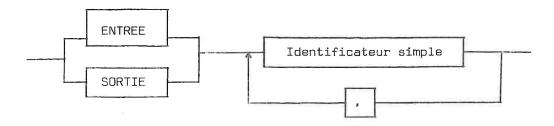

# II.2.1.2. Utilisation des données

Ainsi que nous l'avons vu plus haut, les données utilisées par un module peuvent lui être propres, c'est à dire définies et utilisées par lui-même exclusivement. On les appelle alors variables locales et leur gestion est effectuée par le module lui-même. Elles sont aussi susceptibles d'être mises en correspondance avec les variables d'autres modules (au même titre que les paramètres de sous-programmes par exemple). On distingue alors plusieurs cas :

- variables utilisées par le module en consultation uniquement : on les déclare par la directive : ENTREE liste de variables préalablement apparues dans une déclaration de type.

- variables produites par le module : on les déclare par la directive : SORTIE liste de variables préalablement apparues dans une déclaration de type.

- variables consultées puis modifiées par le module : elles doivent être

déclarées en ENTREE et en SORTIE.

La gestion de ces variables est assurée par le moniteur réparti du réseau selon diverses méthodes en fonction du mode d'utilisation de chacune et des conditions d'activation des modules /42/, /52/.

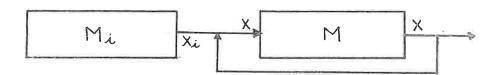

Une utilisation particulière des variables déclarées en entrée et en sortie est celle de variable d'état d'un module itéré : la conservation de cette variable d'état est assurée par le moniteur d'une exécution à l'autre. L'initialisation d'une telle variable devra être effectuée par un module spécifique.

Exemple

$M_{i}$  : module d'initialisation, sortie  $X_{i}$

M : module d'entrée X, de sortie X.

La connexion des modules est alors réalisée ainsi :

Remarquons que dans ce cas d'utilisation, la variable d'état est propre au module, il est donc envisageable de créer une déclaration d'emploi spécifique assurant la protection des variables de ce type vis à vis d'autres modules qui pourraient tenter de la modifier. En effet les déclarations conjointes en entrée et en sortie utilisées actuellement permettent d'assurer la cohérence des accès aux données mais ne permettent pas d'attribuer des droits privilégiés à certains modules.

Les déclarations ENTREE et SORTIE sont aussi utilisées lors de la compilation pour détecter les erreurs de cohérence du programme. C'est ainsi qu'une variable d'entrée ne devra pas être initialiée dans une déclaration de type.

Nous signalons enfin une restriction d'utilisation des variables tableaux, dans la version actuelle du projet, les déclarations ENTREE et SORTIE portent obligatoirement sur le tableau complet.

# II.2.1.3. Attribut Utilisateur

Les déclarations étudiées précédemment permettent d'attribuer à chaque variable un type choisi dans une liste pré-établie. Il peut être intéressant de pouvoir donner à ces variables une qualification supplémentaire :

- amélioration de la lisibilité, et par suite de la maintenabilité des programmes,

- renforcement des contrôles de cohérence lors des interconnexions entre modules (on vérifiera alors la correspondance des qualifications)/42/,

- contrôle de la programmation des modules.

Cela est effectué par les déclarations d'attribut utilisateur. La création et l'utilisation de tels attributs sont entièrement laissées à l'initiative du concepteur /21/.

### Exemple

- (1) ENTIER V1

- (2) REEL V2, I1, I2, I3

- (3) ATTRIBUT VITESSE, INTENSITE

- (4) VITESSE V1. V2

- (5) INTENSITE I1, I2, I3

La ligne (3) correspond à la définition de deux attributs utilisateurs appelés respectivement VITESSE et INTENSITE.

Les lignes (4) et (5) permettent l'attribution de ces qualifications aux variables V1, V2, I1, I2, I3 qui ont déjà fait auparavant l'objet d'une déclaration de type (lignes (1) et (2)).

La plupart des données analogiques manipulées en contrôle de processus industriels étant des grandeurs physiques, il est envisagé de pouvoir décrire l'équation aux dimensions des attributs définis. Cela permettra ensuite à l'analyseur syntaxique de vérifier l'homogénéité des formules et de détecter ainsi les erreurs d'écriture, sources fréquentes d'erreurs.

Une autre extension possible consiste à déclarer, dans chaque module, les unités utilisées pour chaque attribut utilisateur afin de réaliser automatiquement les conversions nécessaires lors des interconnexions de modules.

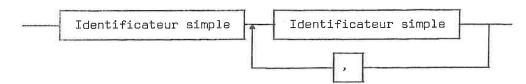

# II.2.2. Les instructions du langage

# II.2.2.1. Expressions et affectations

Les variables et constantes peuvent faire l'objet de diverses opérations et sont combinées en expressions.

On en distingue deux types :

\* les expressions arithmétiques qui utilisent les opérateurs : addition, soustraction, moins unaire, multiplication, division et les parenthésages. Ces expressions combinent les variables entières, entières courtes, réelles et les constantes de même type ; les conversions sont générées automatiquement dans les expressions mixtes.

"les expressions logiques qui portent sur les variables booléennes et les constantes vrai (.V.) et faux (.F.) à l'aide des opérateurs : non, ou, et, ou exclusif des parenthésages ; elles peuvent être également des relations entre deux expres sions à l'aide des opérateurs : >,<,>=,<=,=,#.

Les expressions sont utilisées essentiellement dans les instructions d'affectation :

<Affectation> ::=<Variable simple ou indicée>=<Expression>

L'expression utilisée doit bien sûr être de même type (arithmétique ou logique) que la variable simple ; cela est contrôlé, ainsi que toute tentative d'affectation d'une variable déclarée en entrée et en entrée uniquement (c'est à dire en consultation et non en modification).

Nous ne disposons pas d'affectations multiples (du genre A=B=C) ni d'affectations globales (affectation à un tableau).

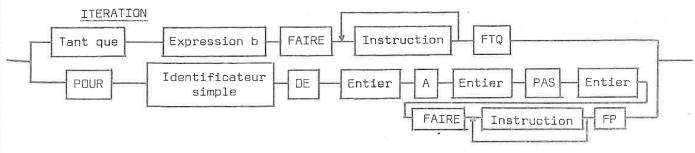

# II.2.2.2. Structures de contrôle

Les structures de contrôle disponibles pour programmer un module (niveau 1) sont :

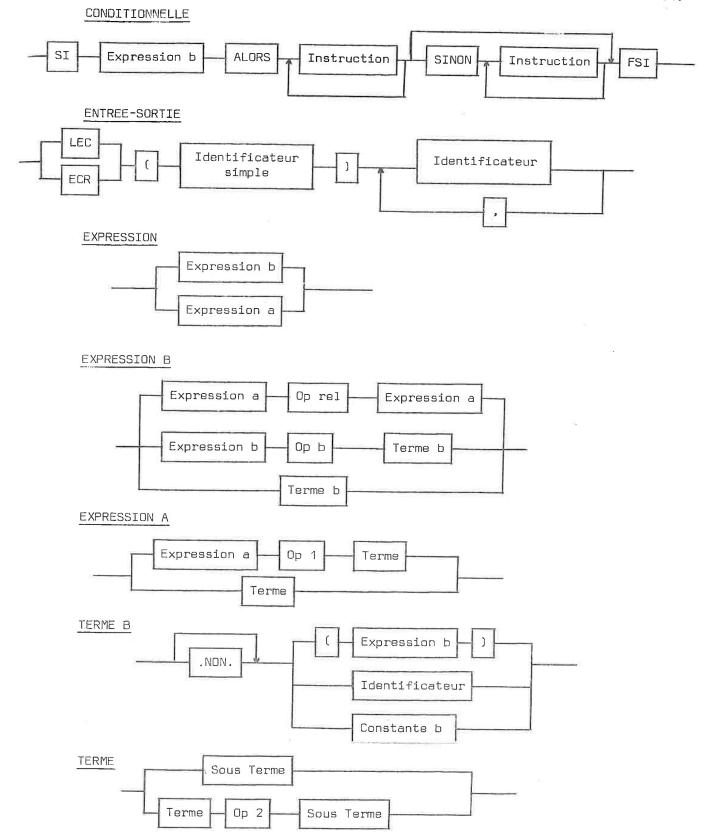

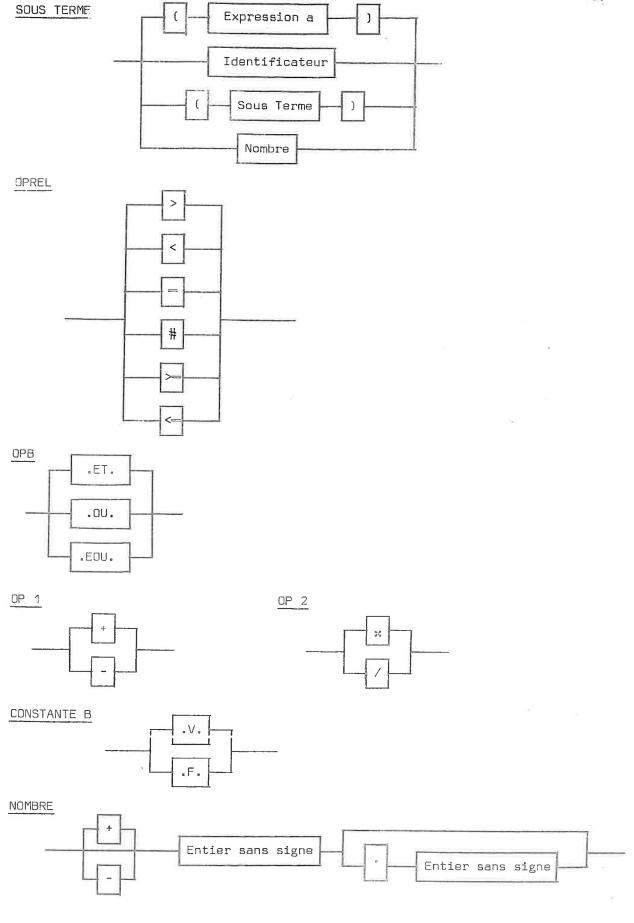

<conditionnelle>::= Si<condition> Alors <S.I.> fsi

Si <cond.> Alors <S.I.> Sinon <S.I.> fsi

<itération> ::= Tant que <cond.> faire <S.I.> ftq

$\underline{Pour}$  <Var. Simple Entière>  $\underline{de}$  <Val 1>  $\underline{\grave{a}}$  <Val 2>  $\underline{pas}$  <Val 3>

faire <S.I.> fp

où <S.I.> représente une séquence d'instructions,

<cond.> une expression booléenne caractérisant la condition à tester

et <Val...> des valeurs numériques.

L'imbrication correcte de ces instructions composées est systématiquement vérifiée.

Les structures offertes sont suffisantes pour programmer tout algorithme ; elles pourraient éventuellement être étendues pour une plus grande simplicité de programmation (instruction "cas" par exemple) /24/.

# II.2.2.3. Ordres d'entrée/sortie

Les périphériques conventionnels et industriels sont atteints dans Sygare par les mêmes instructions : LIRE et ECRIRE. L'utilisation de spécifications "FORMAT" permet au programmeur de préciser les traitements qu'il veut faire subir aux données (mise en page, traitement du signal ... /1/, /2/, /46/. Un module de

Sygare peut atteindre tous les périphériques du réseau, qu'ils soient ou non sur son site d'éxécution. Les problèmes posés par les entrées/sorties et la gestion des périphériques étant très importants, nous les étudierons au chapitre V.

# II.2.2.4. Divers

Le programmeur peut utiliser dans le langage source des fonctions prédéfinies en bibliothèque et qui seront intégrées dans le texte en langage intermédiaire. L'utilisation de telles bibliothèques permet de s'affranchir d'une édition de liens et est donc de mise en oeuvre aisée.

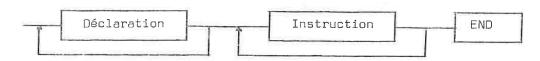

L'arrêt d'un module est obtenu par l'instruction STOP. Nous disposons enfin de deux directives de compilation :

∺ NOM qui permet d'attribuer un identificateur à chaque module

∺ END qui indique la fin du texte source.

## II.2.2.5. Conclusion

Le langage que nous venons de présenter nous semble être un bon compromis entre la simplicité de la programmation et la facilité de génération d'un code objet performant.

Remarquons d'autre part, que la majeure partie des restrictions que nous avons pu signaler sont dues à la réalisation actuelle de Sygare et ne sont pas liées au langage ou à la méthode proposés.

## II.3. LE LANGAGE INTERMEDIAIRE

Le compilateur produit un langage intermédiaire qui doit répondre aux exigences suivantes :

- indépendance vis à vis des sites du réseau (particulièrement en ce qui concerne les adressages de données) mais de niveau assez proche des langages machines pour faciliter la génération de code

- répertoire d'instructions complet (pour la traduction du langage source) mais limité, afin de trouver une traduction aisée sur tout processeur aussi rudimentaire soit-il. (Nous avons cependant admis une restriction : nous travaillons sur des machines à registres).

- conservation du maximum d'informations en provenance du texte source.

Plusieurs possibilités s'offraient pour le choix du langage intermédiaire. On pouvait notamment envisager un langage mono ou multi-opérandes.

On pourrait penser, a priori, qu'un langage à deux ou trois opérandes permet une génération plus performante de code objet car il garde une certaine distance vis à vis des divers processeurs et permet l'utilisation des instructions spéciales souvent disponibles (incrémentation mémoire...). Ces cas sont cependant en nombre relativement limité.

Faute d'une étude exhaustive de toutes les possibilités de génération, les quelques configurations étudiées n'ayant pas fait ressortir d'avantage décisif pour un langage mono ou multi-opérandes, nous avons adopté un langage de type mono opérande car c'est ce type qui se rapproche le plus des langages machine actuels /29/, /30/, /31/. On le trouve d'ailleurs souvent employé lorsqu'un langage intermédiaire se révèle nécessaire /8/, /9/, /10/.

# II.3.1. L'adressage en langage intermédiaire

La comparaison des diverses machines actuellement disponibles montre qu'elles possèdent généralement des jeux d'instructions assez semblables et que les principales disparités viennent des modes d'adressages, notamment avec l'apparition des microprocesseurs qui ont souvent recours à des "astuces" pour dissimuler leurs carence /27/, /28/.

Pour s'affranchir de ces difficultés, il convenait de garder un opérande indépendant des modes d'adressage physiques dans notre langage intermédiaire. Nous l'avons fait en adoptant un adressage symbolique.

L'opérande peut prendre diverses formes :

∺ une constante entière, logique ou réelle

∺ un identificateur de variable simple

\* un identificateur de tableau et un déplacement éventuellement paramétré dans ce tableau (les tableaux sont supposés rangés de manière consécutive, ligne par ligne)

" une adresse de branchement (symbolique).

Les exemples ci-dessous nous montrent quelques représentations en langage intermédiaire de constantes ou variables :

### Exemples :

\*\* Adressage de l'élément de tableau TABL(I,J)

L'opérande intermédiaire correspondant à l'élément de tableau TABL(I,J)

est : TABL + I \* "t₁" + J-"n"

La notation "-" désignant une valeur numérique entière  $\mathbf{t_1} \text{ est la valeur déclarée de la première dimension}$  n vaut :  $\mathbf{t_4}$  + 1

## ☆ Adressage de VECT (2)

On utilise alors l'opérande : VECT + 1

Pour optimiser la génération de code, nous affectuons à la compilation tous les calculs possibles, c'est à dire qui ne sont pas conditionnés par l'implantation sur les sites.

### \* Constantes

La référence à une constante réelle est effectuée à l'aide de l'opérande intermédiaire : C R n

où n est le rang de la constante dans la table des constantes réelles.

Une constante entière sera par contre laissée telle quelle dans le langage intermédiaire pour permettre l'utilisation de l'adressage immédiat chaque fois que cela sera possible et intéressant. Elle sera également rangée dans la table des constantes entières.

### II.3.2. Les instructions du langage intermédiaire

Le langage intermédiaire contient d'une part des instructions exécutables servant à traduire celles du langage source et d'autre part un ensemble de "directives de génération" destinées au générateur de code pour la définition des données et l'organisation générale du binaire qu'il devra produire. Par abus de langage, nous regrouperons ces deux catégories sous le vocable "instructions du langage intermédiaire". Nous pouvons les répartir en plusieurs classes :

- \* Manipulation des registres de travail :

- rangement de registre : R A N

- chargement de registre : C H A

- ™ Opérations arithmétiques et logiques

- addition : A D D

- soustraction : S O U

- négation (complément à 2) : N G T

- multiplication : M U L

- division : D I V

- ou inclusif : O U

- ou exclusif : E-O U

- complémentation : N O N

- et : E T

## ∺ Tests et branchements

- comparaison : C M P

- branchement inconditionnel : B R A

- branchement conditionnel : B E branchement si égal

BNE " différent

B I " inférieur

BIE " inférieur ou égal

B S " supérieur

BSE " " ou égal.

Cet ensemble d'instructions est utilisé pour la traduction des diverses structures de contrôle.

## ∺ Gestion de sous-programmes

- branchement : BSP

- retour : R S P

Ces instructions seront employées lors de l'utilisation des fonctions de bibliothèque.

≍ Arrêt du programme : S T O P

∴ Insertion d'étiquette : E P C

Cette directive est utilisée pour insérer dans le texte intermédiaire des adresses de branchements lors de la traduction des structures de contrôle du langage source. Elle constitue uniquement un point de repère et ne donnera lieu à aucun code objet.

- " Instructions d'entrée/sortie

- entrée : LIR

- sortie : E C R

Ces deux instructions correspondent aux instructions équivalentes du langage source. Leurs opérandes n'obéissent pas aux règles du langage intermédiaire ; ils sont obtenus par recopie et simplification du texte source et feront l'objet d'un traitement spécial du générateur de code.

### \* Directives de définition de données

- définition de constante réelle : C R

- définition de constante entière : C E

- définition de zone de travail : M A N

- définition de variables simples utilisées localement : V L O C

- définition de tableaux utilisés localement : T L O C

- définition de variables et tableaux utilisés en entrée et/ou sortie : VCOM

Ces directives seront étudiées en détail dans le chapître consacré à la génération de code.

## II.3.3. Caractéristiques du langage intermédiaire

Les instructions de notre langage intermédiaire sont indépendantes du type, et a fortiori de la représentation physique des variables manipulées.

## Exemple:

Dans le contexte :

REEL A(6), B, C(3)

ENTIER D,I

L'affectation :

A(5) = B+C(I)+D

correspondra à la séquence intermédiaire :

CHA B

ADD C+I-1 C(I) variable réelle

ADD D D variable entière

RAN A+4

L'instruction ADD est utilisée aussi bien pour les variables entières que réelles, rangées sur un ou plusieurs mots.

Le nombre et la nature des registres disponibles sur la machine d'exécution conditionnent la stratégie d'allocation retenue, et par là-même, l'efficacité du code objet généré /20/. Ces paramètres ne sont cependant pas connus au niveau du langage intermédiaire ; c'est pourquoi nous avons choisi de travailler sur une machine virtuelle possédant un nombre illimité de registres. C'est le générateur code qui devra gérer les registres de la machine cible et effectuer les sauvegardes éventuellement nécessaires.

### Exemple:

L'affectation du langage source :

$A = (B+C) \times (D+E)$

donne en langage intermédiaire :

```

CHA B (B) \rightarrow Reg 1

ADD C (Reg 1) + (C) \rightarrow Reg 1

CHA D (D) \rightarrow Reg 2

ADD E (Reg 2) + (E) \rightarrow Reg 2

MUL (Reg 2) * (Reg 1) \rightarrow Reg 1

RAN A (Reg 1) \rightarrow A

```

où:

∺(-) représente le contenu associé à l'adresse spécifiée

imes o représente un transfert

Reg n représente le n registre de travail utilisé.

Un code opération non suivi d'opérande correspond à une opération entre deux registres de travail (ici c'est le cas de MUL).

Le langage que nous venons de présenter est facilement traduisible sur n'importe quelle machine du fait de son jeu limité d'instructions choisies pour leur adaptation aux structures courantes de processeurs. Il est cependant sémantiquement complet et permet donc de traduire toute extension éventuelle du langage source. L'utilisation de diverses directives de génération permet de conserver au niveau intermédiaire les diverses informations fournies par le langage source (déclarations ...).

CHAPITRE III

LA COMPILATION DANS SYGARE

### CHAPITRE III

### LA COMPILATION DANS SYGARE

### III.1. INTRODUCTION

La compilation dans Sygare a pour but de transformer le langage source utilisé pour la description des modules, en langage intermédiaire assimilable par le générateur de code.

Le travail effectué à ce niveau comporte deux phases principales :

"Une analyse lexicographique permettant de créer et mettre à jour la table des symboles, ainsi que de vérifier l'emploi correct de chaque symbole.

"Une génération des instructions intermédiaires en fonction des instructions du texte source, avec intervention de l'analyseur syntaxique pour l'évaluation des expressions /10/, /11/, /12/, /13/.

Les informations recueillies lors des traitements du texte source seront, dans la mesure du possible, communiquées au générateur de code sous forme de directives de génération.

Un effort tout particulier est apporté lors de la compilation, pour la détection des erreurs de programmation.

## III.2. LA COMPILATION

La structure du compilateur est assez simple, le texte source est traité instruction par instruction dans l'ordre de lecture et en une seule passe /11/.

# III.2.1. Traitement des déclarations

Les déclarations permettent de construire et de mettre à jour la table des symboles du compilateur.

Les déclarations de type servant à définir les variables, à leur rencontre le compilateur va élaborer le descripteur des nouvelles variables et le rajouter à la suite de la table des symboles en vérifiant qu'il n'y a pas de double

définition. Le descripteur d'une variable est un pavé de six mots de seize bits ayant la structure suivante :

| 0 | N                                            | N |

|---|----------------------------------------------|---|

| 1 | N                                            | N |

| 2 | N                                            | N |

| 3 | Т                                            | Р |

| 4 | <sup>T</sup> 2                               |   |

| 5 | b <sub>1</sub> b <sub>2</sub> T <sub>1</sub> |   |

N : identificateur de la variable : de 1 à 6 caractères alphanumériques ASCII

T : codage du type physique de la variable (1 octet)

T = 0 entier

T = 1 booléen

T = 2 réel

T = 3 entier court

la place disponible dans l'octet peut être utilisée pour le codage de l'attribut utilisateur s'il existe.

P: conditions d'utilisation de la variable (1 octet)

P = 0 variable locale

$P = (80)_{16}$  variable en entrée

$P = (40)_{16}$  variable en sortie

P = (CO)<sub>16</sub> variable en entrée et sortie

$^{\rm T}_{\rm 1}$  et  $^{\rm T}_{\rm 2}$  : éventuellement dimensions des tableaux selon les indications des bits b  $_{\rm 1}$  et b  $_{\rm 2}$  :

$b_1b_2 = 00$  variable simple :  $T_1 = 1$ ,  $T_2 = 0$

$b_1b_2 = 10$  tableau monoindice:

$T_1$  - dimension,  $T_2 = \bar{0}$

$b_1b_2 = 11$  tableau bi-dimensionnel :

$T_1$  = dimension 1,  $T_2$  = dimension 2.

Ces deux derniers mots permettent de vérifier que l'emploi des variables est compatible avec leur déclaration.

Le compilateur utilise également les déclarations pour préparer les directives de génération (et éventuellement d'initialisation) de variables (directives TLOC, VLOC, VCOM).

### III.2.2. Traitement des instructions composées

Le traitement des instructions composées est effectué à l'aide d'une pile /11/, /13/, permettant de conserver deux informations :

st la liste des composants élémentaires des instructions composées et leur ordre d'apparition, ce qui permet de détecter les erreurs d'imbrication

les adresses des branchements qui devront être générées au niveau du langage intermédiaire.

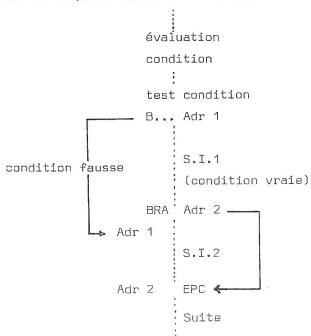

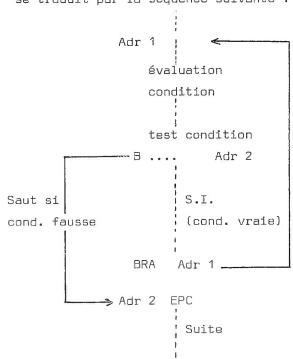

Examinons à titre d'exemple le traitement du Si ... alors ... Sinon... et du tant que ... faire :

## 1 <u>Si</u> cond <u>Alors</u> S.I.1 <u>Sinon</u> S.I.2 <u>fsi</u>

donnera la séquence suivante en langage intermédiaire : (S.I.) = Séquence instructions)

Le traitement de la pile donne alors :

Sur le "Si ... Alors" : empilement de l'adresse Adr 1 de branchement si la

condition est fausse:

Si Adr 1

Alors

Sur le "Sinon" : vérification de la présence du "Si... Alors" et empilement de l'adresse Adr 2 de sortie :

| Si Adr 1 |

|----------|

|          |

| Alors    |

Sur "fsi" nous vérifions la présence du "Si ... Alors" et du "Sinon" (éventuellement) et nous dépilons ces mots.

2 <u>Tant que</u> cond <u>faire</u> S.I. <u>ftq</u> se traduit par la séquence suivante :

Nous utiliserons cette fois deux mots de la pile à la rencontre de "tant que... faire" où nous rangerons l'adresse Adr 1 de branchement pour l'évaluation de la condition de fin d'itération et l'adresse Adr 2 de fin d'itération.

| faire       | Adr 2 |

|-------------|-------|

| tant<br>que | Adr 1 |

|             |       |

A la rencontre de "ftq" nous vérifions que la pile présente une configuration correcte et nous dépilons deux mots.

### III.2.3. Traitement des expressions

Le traitement des expressions est effectué en deux temps :

\*\*Une analyse lexicale de l'expression permettant de déterminer si toutes les variables sont bien déclarées et correctement utilisées et de détecter la plupart des erreurs d'écriture. Lors de cette analyse, le texte source est modifié pour simplifier les traitements ultérieurs ; de plus il donne lieu à la création d'une table d'analyse dont l'organisation est la suivante :

|    | Op. 1 | බ 1<br>බ 2 |

|----|-------|------------|

| // | //    | 1          |

|    | Op. i | a i        |

| :  |       |            |

Les octets de poids fort de chaque mot représentent la suite des opérateurs mis en évidence dans l'expression, alors que les octets de poids faible indiquent l'emplacement, dans le texte source, des opérandes suivant chaque opérateur. En cas d'opérateurs consécutifs, ce pointeur est mis à zéro.

☼ Une analyse syntaxique qui n'est effective que si aucune erreur n'a été

détectée à l'étape précédente /14/.

L'analyseur syntaxique est réalisé assez simplement. Les opérateurs sont munis de relations de priorité entre eux (représentées sous forme de matrice (fig. III.1). On explore la table d'analyse de manière séquentielle en considérant les opérateurs par couples :

(Op. 1, Op. 2), (Op. 2, Op.3), ... (Op.

$$_{j}$$

, Op. $_{j+1}$ )

Jusqu'à la rencontre d'un couple tel que  ${\rm Op.}_{i+1}$  force le traitement de  ${\rm Op.}_i$ , ce qui nous est indiqué par consultation de la matrice de priorité. Nous noterons, dans la suite du texte, cette relation sous la forme :

$$Op_{i+1} > Op_{i}$$

(Op<sub>i+1</sub> force le traitement de  $Op_{i}$ )

Après le traitement de Op. , on l'élimine de la table ainsi que les opérandes utilisés, et on reprend le processus de comparaison en remontant la table, avec les couples :

$$(Op._{i-1}, Op._{i+1}), (Op_{i-2}, Op._{i+1})$$

S'il n'y a plus d'opérateur à traiter avant le rang i+1, ou si aucun ne vérifie la relation :  $\text{Op.}_{i+1} \bigvee_{i \neq i} \text{Op.}_{j}$

| b           | Déb | + | - | ж | / | ( | ) | NON | OU<br>EXCL | ou  | ET | U | < | > . | # | = |

|-------------|-----|---|---|---|---|---|---|-----|------------|-----|----|---|---|-----|---|---|

| Début       | \   | 0 | 0 | 0 | 0 | 0 | 0 | o   | ٥          | . 0 | 0  | 1 |   | \   | \ | \ |

| +           | 0   | 1 | 1 | 0 | 0 | 0 | 1 | \   | \          | \   | \  | 1 | 1 | 1   | 1 | 1 |

| _           | 0   | 1 | 1 | 0 | 0 | 0 | 1 | \   | \          | \   | \  | 1 | 1 | 1   | 1 | 1 |

| ×           | 0   | 1 | 1 | 1 | 1 | 0 | 1 | \   | \          | \   | \  | 1 | 1 | 1   | 1 | 1 |

| 1           | 0   | 1 | 1 | 1 | 1 | 0 | 1 | \   | \          | \   | \  | 1 | 1 | 1   | 1 | 1 |

| (           | 0   | 0 | 0 | 0 | 0 | 0 | 1 | 0   | 0          | ٥   | 0  | 1 | 1 | 1   | 1 | 1 |

| )           | 0   | 1 | 1 | 1 | 1 | 0 | 1 | 0   | 1          | 1.  | 1  | 1 | 1 | 1   | 1 | 1 |

| NON         | 0   |   |   | \ |   | 0 | 1 | 1   | 1          | 1   | 1  | 1 | \ | \   | 1 | 1 |

| OU<br>EXCL. | 0   | \ | \ | \ | \ | 0 | 1 | 0   | 1          | 1   | 1  | 1 | \ | \   | 1 | 1 |

| טט          |     | \ |   |   | \ | 0 | 1 | 0   | 1          | 1   | 1  | 1 | \ | \   | 1 | 1 |

| ET          |     |   |   | \ | \ | 0 | 1 | 0   | 1          | 1   | 1  | 1 | \ | \   | 1 | 1 |

| U           |     |   |   |   |   |   |   |     |            |     |    |   |   |     |   |   |

| <           |     |   |   |   |   |   |   |     |            |     |    |   |   |     |   |   |

| >           |     |   |   |   |   |   |   |     |            |     |    |   |   |     |   |   |

| #           |     |   |   |   |   |   |   |     |            |     |    |   |   |     |   |   |

| =           |     |   |   |   |   |   |   |     |            |     |    |   |   |     |   |   |

Fig.III.1. Matrice de relation des opérateurs

Un "1" signifie que l'on a la relation : Op. > Op. b

le processus reprend séquentiellement :

$$(0p._{i+1}, 0p._{i+2}), (0p._{i+2}, 0p._{i+3}) \dots$$

Lorsque la condition de fin est rencontrée, on vérifie qu'aucun opérateur n'a été oublié (ce qui serait dû à une erreur de syntaxe).

Le traitement des opérateurs est effectué de la façon suivante :

"Parenthèses : gestion d'un compteur permettant de vérifier l'imbrication correcte de sous-expressions parenthésées et positionnement des pointeurs pour la reprise de l'analyse.

"Début d'expression : le traitement de ce pseudo opérateur correspond en fait à la fin d'analyse de l'expression et provoque selon les cas l'affectation (instruction d'affectation) ou l'évaluation de la relation (expressions logiques).

" Opérateurs arithmétiques et logiques : le traitement est commun pour tous les opérateurs arithmétiques ou logiques binaires ; il est décrit par l'algorithme suivant :

$\underline{\mathtt{Si}}$  il existe un opérande précédent et un opérande suivant

Alors générer

CHA O.P. (opérande précédent)

CODE O.S. (opérande suivant)

Sinon si il existe un opérande suivant

Alors générer

CODE O.S.

Sinon si il existe un opérande précédent

alors si opérateur commutatif

alors générer

CODE O.P.

Sinon générer

CHA O.P.

CODE

fsi

Sinon (il n'existe ni précédent, ni suivant)

générer :

CODE

fsi

fsi

On désigne par opérande précédent, s'il existe, un opérande non encore traité situé dans la table d'analyse entre l'opérateur en cours de traitement et le premier opérateur non encore traité le précédant. La définition est symétrique pour l'opérateur suivant. CODE représente l'instruction du langage intermédiaire exprimant la fonction demandée par l'opérateur.

Les opérateurs unaires sont toujours générés sous la forme CODE précédée si nécessaire d'une instruction de chargement.

Lors du traitement des expressions, le compilateur gère les tables des constantes entières et des constantes réelles en y inscrivant, si elles n'y figurent pas déjà, les constantes rencontrées en cours d'analyse. On inscrit de même dans la table des constantes entières, toutes les constantes élaborées lors des calculs d'adresse.

### III.2.4. Traitement des entrées/sorties

Les instructions d'entrée-sortie disponibles au niveau du langage intermédiaire constituent une forme simplifiée de celles disponibles dans le langage source. Le traitement de ces instructions va donc simplement consister en la transformation de l'ordre source en une série d'opérations élémentaires d'entrée/sortie avec réarrangement des paramètres concernant chaque opération.

Il n'est pas possible de traiter plus avant ces instructions, car le mode d'appel du moniteur d'entrée-sortie, le nombre, la nature et le mode de passage des paramètres nécessaires pour ces opérations, sont largement influencés par la machine cible /35/.

#### III.2.5. Divers

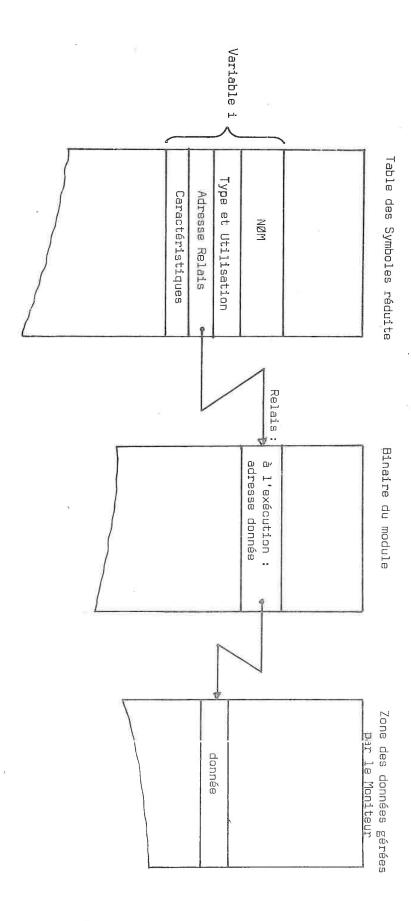

Lors de la rencontre de la directive END, le compilateur effectue un réarrangement de ses informations en vue du traitement ultérieur par le générateur de code et par le moniteur d'exécution (ce travail n'est effectué que dans le cas où la compilation s'est passée sans erreurs). La table des symboles est condensée par élimination des variables locales et forme alors le bloc de traitement qui sera utilisé par le moniteur d'exécution lors des interconnexions entre modules (déclarations de connexion des variables). Les tables des constantes sont scrutées pour créer les directives de génération de constantes entières et réelles utilisées par le générateur de code.

Le compilateur crée enfin un fichier portant le nom du module et dans lequel il va ranger les trois catégories d'informations qu'il a préparées, à savoir :

- ∺ directives de génération de variables et de constantes

- ∺ programme en langage intermédiaire

- ∺ table des symboles réduites.

## III.2.6. Conclusion

Lors de la compilation, nous avons effectué un contrôle constant des erreurs de programmation : erreurs d'écriture, erreurs de syntaxe, mauvaise utilisation des variables indicées, mélange de types interdit, erreurs de cohérence, mauvaise imbrication d'instructions composées. Nous disposons alors à la fin de celle-ci de tous les éléments nécessaires à la génération de code objet sur les divers sites du réseau.

Les textes intermédiaires des modules sont archivés sur le site de production et seront utilisés lorsque l'opérateur aura fixé la répartition de son application. Ils seront également employés lors d'une éventuelle reconfiguration de l'application.

Nous n'avons pas rencontré de difficulté notable dans la traduction du langage source en langage intermédiaire, ce qui semble indiquer que ce dernier est bien adapté à nos besoins.

# CHAPITRE IV

LA PRODUCTION DE CODE EXECUTABLE

#### CHAPITRE IV

#### LA PRODUCTION DE CODE EXECUTABLE

### IV.1. PRINCIPE RETENU

Le réseau, pour lequel nous désirons fournir du code objet, peut être composé de matériels très divers : mini-ordinateurs, microprocesseurs, processeurs spécialisés (entrées/sorties, traitement du signal ...) et la génération est de ce fait plus compliquée que dans le cas où les machines choisies sont de caractéristiques voisines /8/, /9/, /10/, /25/.

Un générateur de code devra réaliser le travail suivant :

- \* Structuration et adaptation des données (variables simples, tableaux, constantes) en fonction de leur format, de leur type et de la représentation interne prévue pour le traitement dans la machine cible. Il faudra également tenir compte à ce niveau des moyens disponibles pour atteindre ces données (prévoir par exemple les relais d'adressage indirect).

- \* Traduction des instructions du langage intermédiaire en langage machine en fonction du répertoire d'instructions disponible sur la machine cible (il faudra éventuellement simuler les instructions n'existant pas, ce qui est le cas par exemple pour MUL et DIV sur de nombreux microprocesseurs. Cette traduction devra tenir compte du type de l'opérande manipulé, de sa représentation interne dans la machine considérée, des registres de travail disponibles et du contexte (génération éventuelle de sauvegardes de registres).

- "Adaptation des fonctions d'accès aux opérandes en fonction de leur type, de leur structure, de leur représentation interne, des adressages disponibles sur le site considéré et enfin du répertoire d'instructions.

- » Génération des séquences d'initialisation propres à chaque site : chargement initial de registres, bases, pointeurs, définition de pile ..., des séquences de communication avec le moniteur du réseau et avec le moniteur d'entrées/sorties (méthode de passage des paramètres).

- st Gestion des conversions automatiques lors du calcul d'expressions mixtes.

- st Mise à jour de la table des variables partagées en fonction des conditions d'implantation sur le site.

- $^{ imes}$  Optimisation éventuelle du code, et en particulier allocation des registres /19/, /20/.

Pour atteindre ces objectifs, deux possibilités s'offraient à nous ;

"Utiliser un générateur autonome par type de site du réseau. Cette solution est peu intéressante car elle manque de souplesse en cas de modification du réseau : il faut écrire à chaque fois un nouveau générateur ce qui n'est pas toujours facile. De plus, une partie des traitements est commune aux divers sites, il y a donc redondance.

" Utiliser un générateur unique dont le fonctionnement est paramétré par les caractéristiques de la machine cible.

Nous avons opté pour cette dernière solution, et plus précisément pour sa réalisation sous forme d'un macro-processeur /25/.

Nous rappelons qu'un macro-processeur est un processeur capable d'effectuer de la substitution paramétrée de texte. Dans notre cas, il devra en outre effectuer cette substitution de manière conditionnelle, et il aura à gérer et mémoriser divers événements destinés à permettre la gestion du contexte de génération /44/.

Le macro-processeur peut nous donner directement du binaire objet, cependant nous avons préféré passer par une étape symbolique supplémentaire : le langage d'assemblage de chaque site. Cette méthode facilite la mise au point de la phase de génération et permet également de bénéficier de logiciel déjà existant.

La génération de code est alors constituée des deux étapes suivantes :

- \* Transposition du langage intermédiaire en langage d'assemblage du site considéré par le macro-processeur

- $^{ imes}$  Assemblage (et éventuellement translation) qui nous donne le binaire exécutable.

Les macro instructions du macro-processeur sont constituées par les directives de génération, les instructions du langage intermédiaire et les structures des opérandes intermédiaires (pour la génération de la fonction d'accès associée).

Les macro-définitions ou définition du texte et des paramètres associés aux macro-instructions constituent une bibliothèque propre à chaque site et à chaque type de code généré. En effet, les macro-définitions sont d'écriture relativement simple, on peut donc en prévoir répondant à divers critères de code généré : mode mise au point, mode rapide, mode peu volumineux ...

Il convient de remarquer cependant que ces jeux de macro-définitions doivent être écrits avec soin car c'est d'eux que dépendent en grande partie les performances du code généré, ainsi que nous le verrons sur quelques exemples.

On peut envisager, dans un but de simplification, l'automatisation de l'écriture de ces macro-définitions par un pré-traitement partant des caractéristiques de la machine cible données dans un langage de description approprié (cette simplification risque de se faire au détriment des performances) /30/, /33/.

L'algorithme de génération découle directement des choix effectués lors de l'analyse syntaxique, il est valable pour tous les sites et se combine avec l'algorithme d'allocation de registres qui est propre à chaque machine :

Si code instruction n'est pas CHA ou RAN

Alors Si instruction possède un opérande

Alors traitement de l'opérande, génération de la méthode d'accès

(avec si nécessaire application de l'algorithme d'allocation lors des calculs d'adresse)

Choix du code machine et génération de l'instruction

Sinon Si instruction précédente est CHA

Alors utiliser comme opérande la donnée manipulée avant l'instruction

CHA (on a affaire à une instruction non commutative, il faut

respecter l'ordre des opérandes)

Sinon Si instruction commutative

Alors effectuer opération entre les deux dernières données dans l'ordre le plus commode

Sinon effectuer opération entre les deux dernières données en respectant l'ordre d'évaluation

fsi

fsi

fsi

Sinon Si instruction est CHA

Alors effectuer le chargement de registre en fonction de l'algorithme d'allocation

$\underline{\operatorname{Sinon}}$  (instruction est RAN) effectuer le rangement et libérer les registres  $\underline{\operatorname{fsi}}$

fsi

Cet algorithme n'est pas appliqué aux instructions spéciales : entrées/sorties, branchements, instructions implicites (n'ayant jamais d'opérande) qui sont générées directement en fonction des possibilités du site.

Le résultat de la génération de code est un fichier directement exploitable par le moniteur d'exécution et comportant les trois zones suivantes :

\* le code binaire exécutable du site concerné, tel qu'il vien d'être élaboré par le générateur

∺ un descripteur du code (taille, point d'entrée ...)

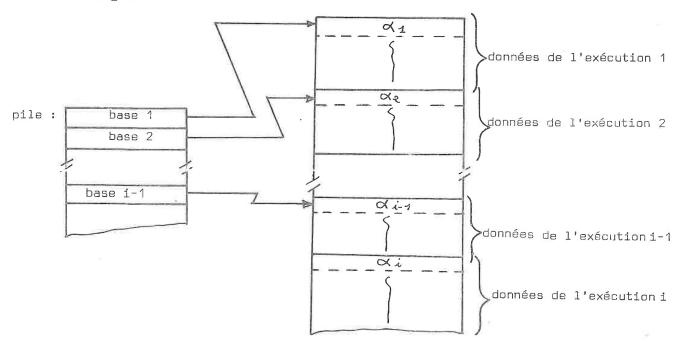

\* la table des symboles réduite provenant de la compilation et mise à jour pour permettre l'accès aux données gérées par le moniteur. Celui-ci y trouvera l'adresse, dans le module, d'un relais local qu'il initialisera avant chaque exécution avec l'adresse effective de la donnée (Fig.IV.1) /42/.

Fig.IV.1. Accès aux données gérées par le moniteur.

#### IV.2. ETUDE DE QUELQUES CAS DE GENERATION

Nous allons maintenant préciser sur quelques cas concrets les points esquissés dans le paragraphe précédent, en mettant en valeur les problèmes auxquels nous sommes confrontés et les compromis adoptés. Les machines étudiées ont été choisies pour leur disponibilité, permettant de tester les solutions retenues ; et pour leur diversité dans les caractéristiques que nous rappellerons brièvement.

## IV.2.1. Cas du Solar 16/40 S.E.M.S.

### IV.2.1.1. Présentation du matériel

Le Solar 16/40 est un minicalculateur dit "industriel" à mots de seize bits. Il dispose d'un jeu très complet d'instructions permettant des manipulations en mémoire, dans les registres, entre registres, entre registres et mémoire. Il est également capable de travailler au niveau de l'octet et du bit de manière plus restreinte /37/.

Nous y trouvons plusieurs mode d'adressage :

- relatif à une parmi trois bases

- immédiat

- indirect

- indirect post indexé

- relatif au compteur ordinal pour les branchements.

Nous disposons de quatre registres de travail :

- A : accumulateur

- B : extension d'accumulateur

- X : registre d'index ou de travail

- Y : registre de travail.

Ce site est aussi caractérisé par un processeur de virgule flottante câblé.

IV.2.1.2. Représentation des données et fonctions d'accès

Les quatre types de données sont représentés ainsi :

" entiers : sur un mot (16 bits), c'est la représentation naturelle sur le Solar, il n'y a donc pas de problème.

∺ courts : ils sont représentés sur les 8 bits de poids faible d'un mot, leur utilisation sera cependant identique à celle des entiers car les instructions sur octet sont en nombre limité et leur utilisation serait pénalisante en temps et en occupation mémoire.

∺ booléens : ils seront aussi représentés sur 16 bits, les opérations logiques disponibles sur la machine travaillant sur les 16 bits en parallèle.

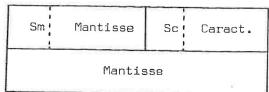

pprox réels : représentés sur 32 bits selon la convention de l'opérateur flottant :

Mantisse : 23 bits + signe (Sm) Caractéristique : 8 bits+signe(Sc)

L'accès aux diverses variables est fonction de leur utilisation et de leur structure :

- st variables simples locales : on les atteint par adressage direct (basé)

- " variables simples gérées par le moniteur : on emploie cette fois l'adressage indirect via un relais positionné par le moniteur lors de l'interconnexion des modules

\* tableaux locaux ou non : l'adressage indirect post indexé est utilisé. Le relais d'indirection est, selon le cas, défini localement ou par le moniteur. Le registre d'index permet de préciser le déplacement dans le tableau qui a évolué à chaque fois.